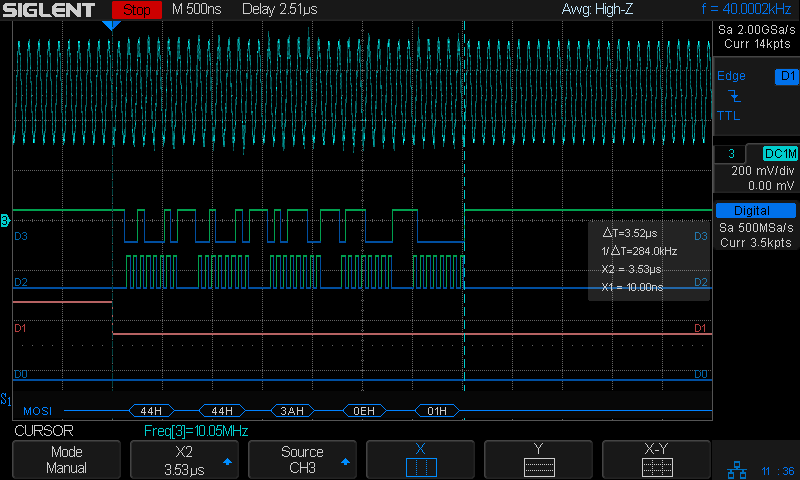

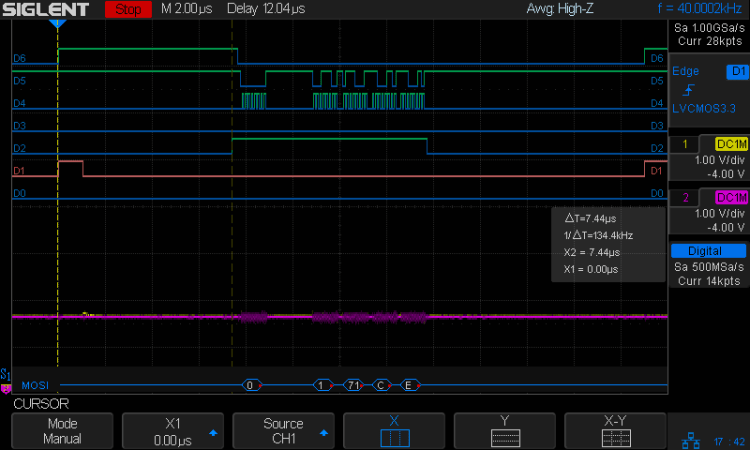

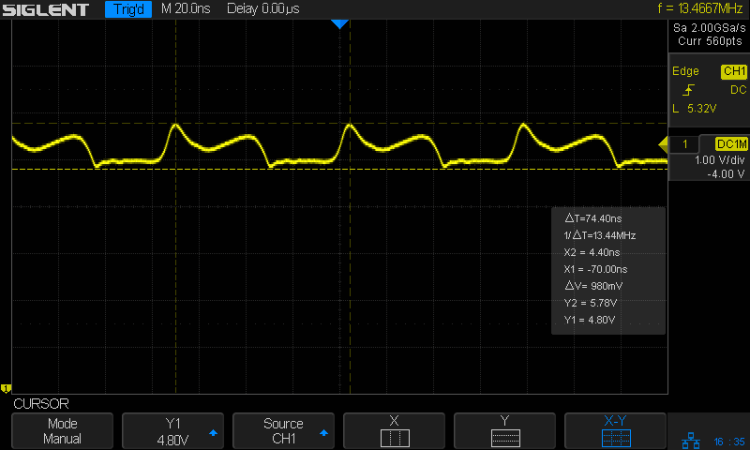

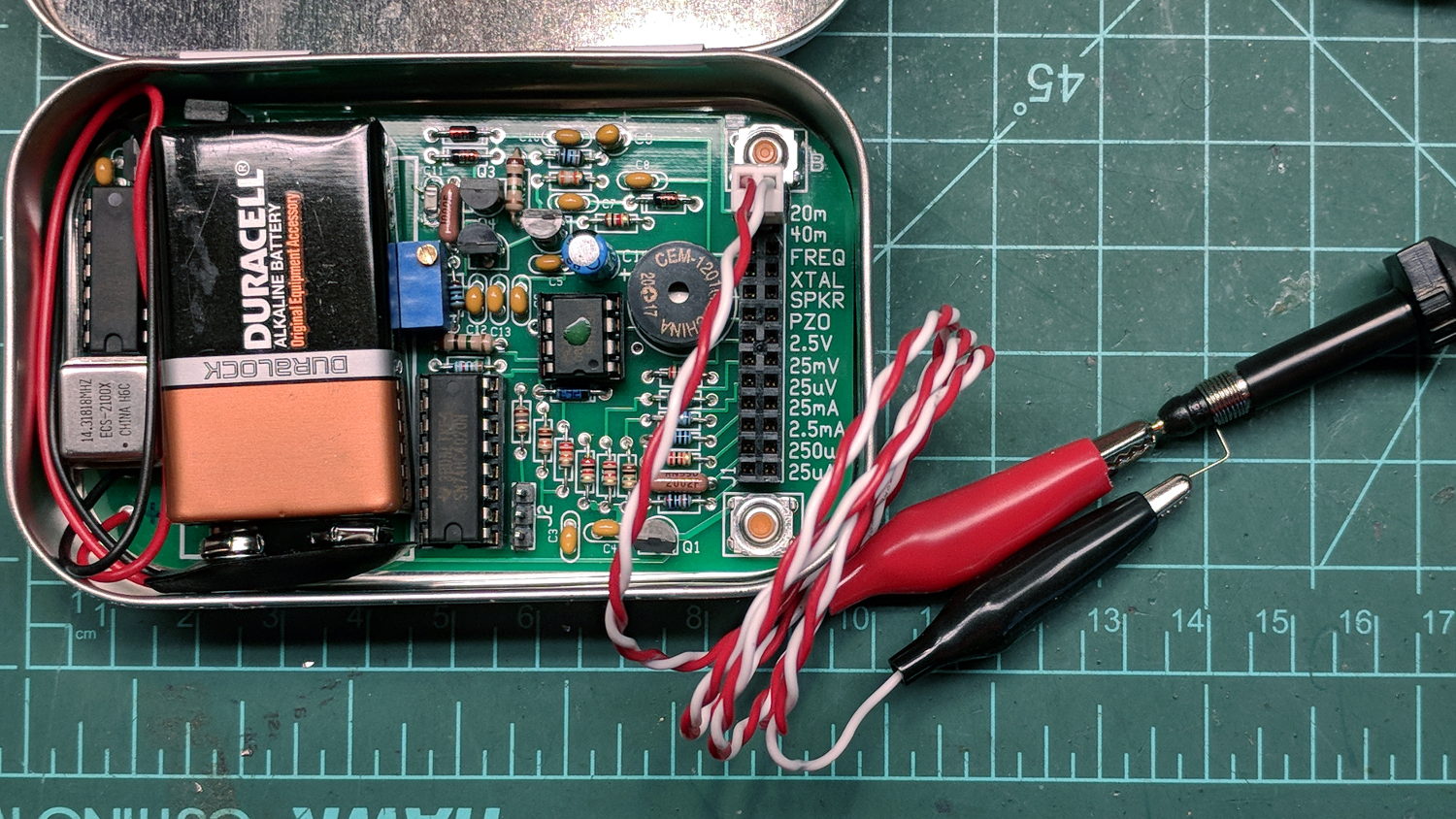

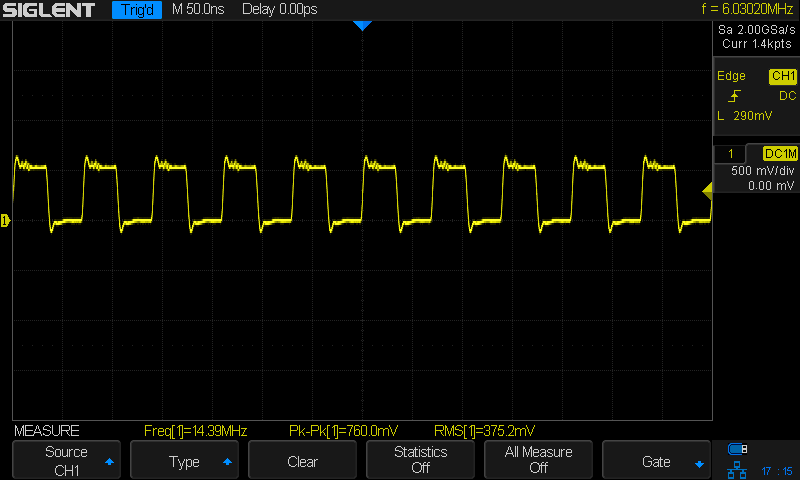

The QRPme Pocket Pal II produces RF test signals in the 20 meter and 40 meter bands, both square-ish waves derived from its 14.31818 MHz oscillator-in-a-can:

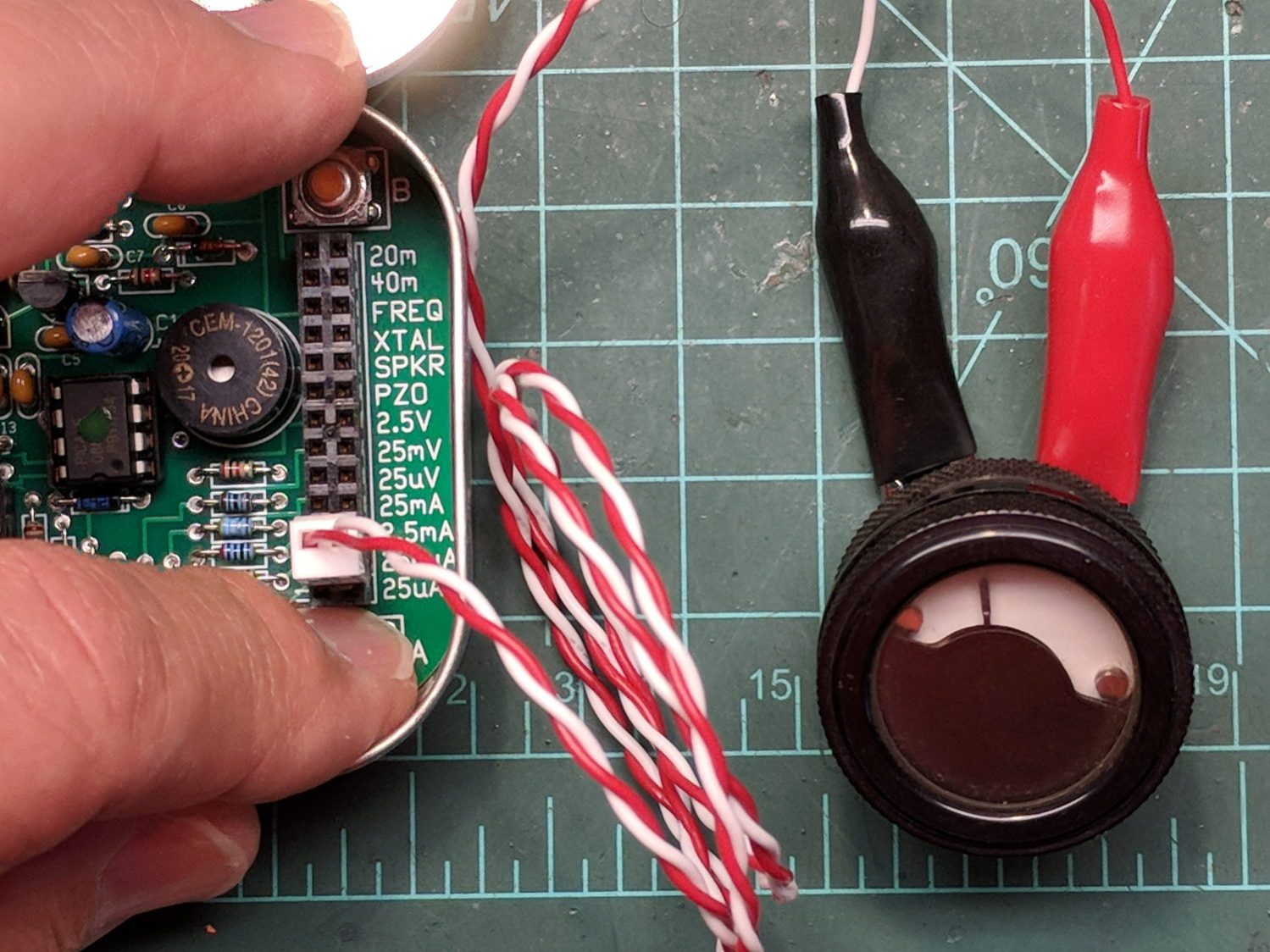

That’s the 20 meter signal, seen through the twisted pair test lead with alligator clips clamped on the scope probe, thusly:

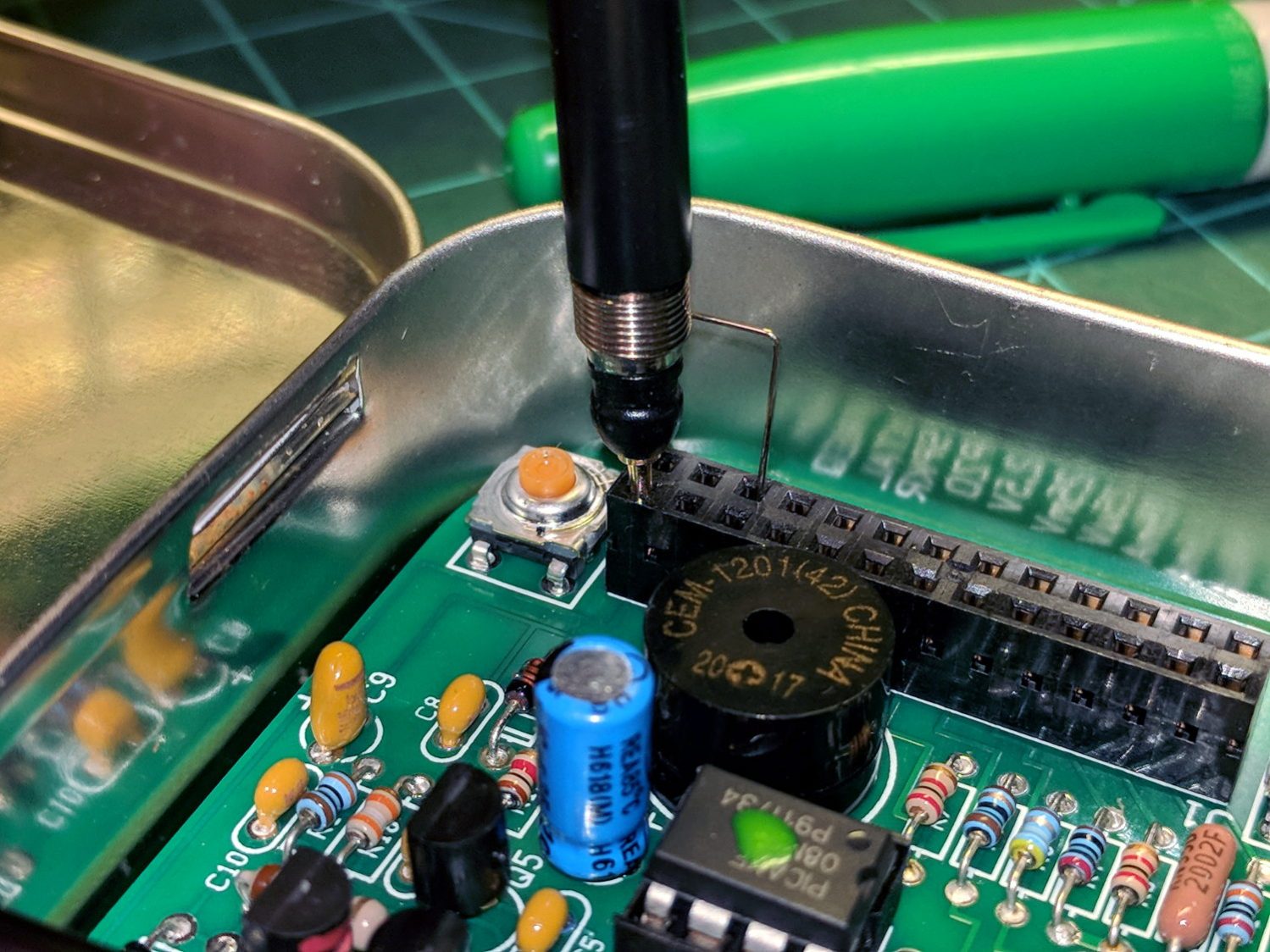

When you’re working with RF signals, the “ground” part of the probe circuit matters:

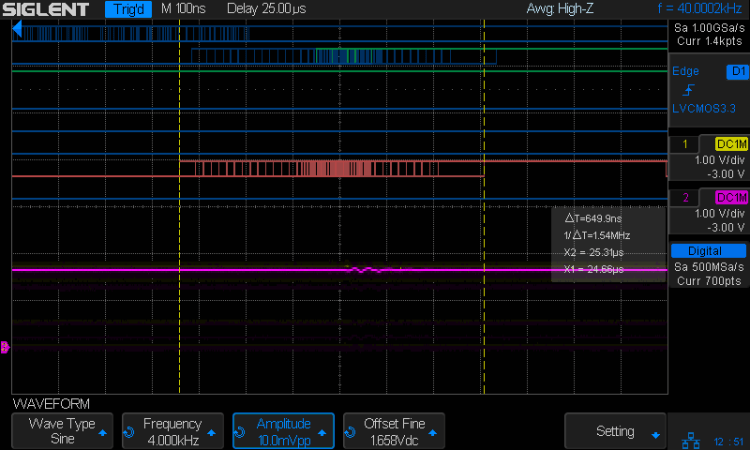

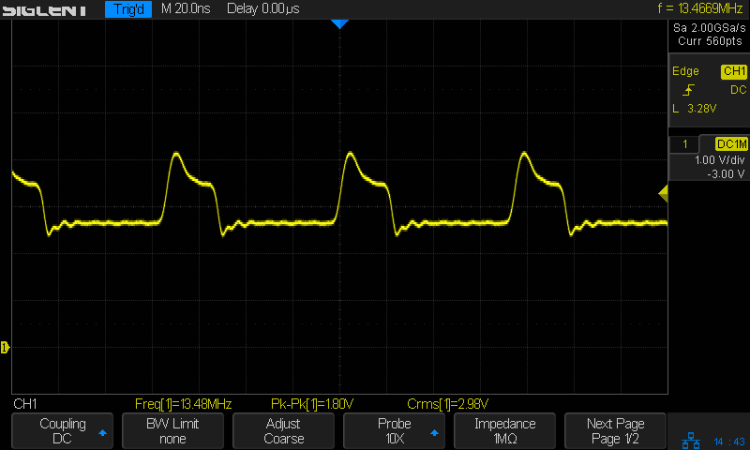

That’s with the probe and its short spring ground jammed directly into the header:

Well, in this case, signal quality doesn’t matter very much, as you’re using the Pocket Pal II at a hamfest (or your bench) to determine if an HF radio is completely dead.

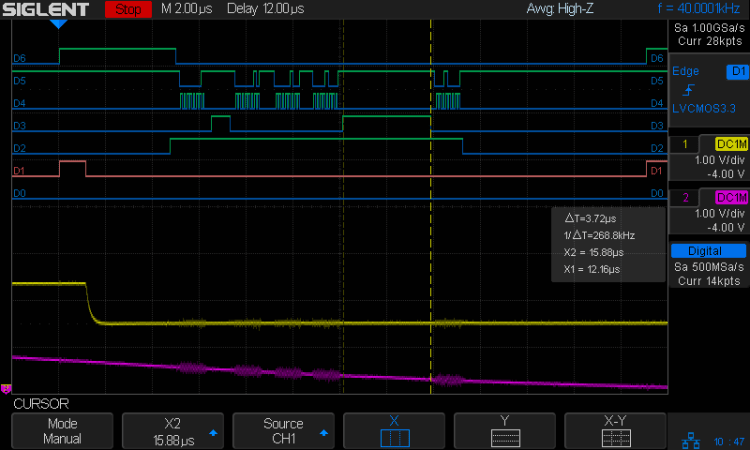

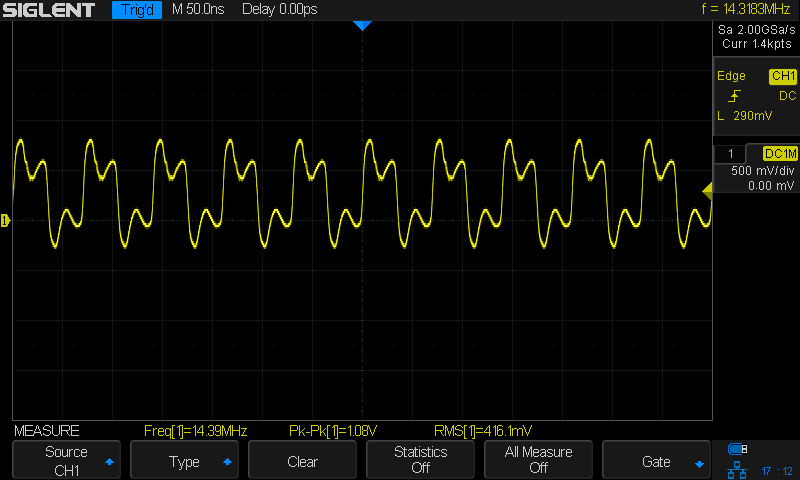

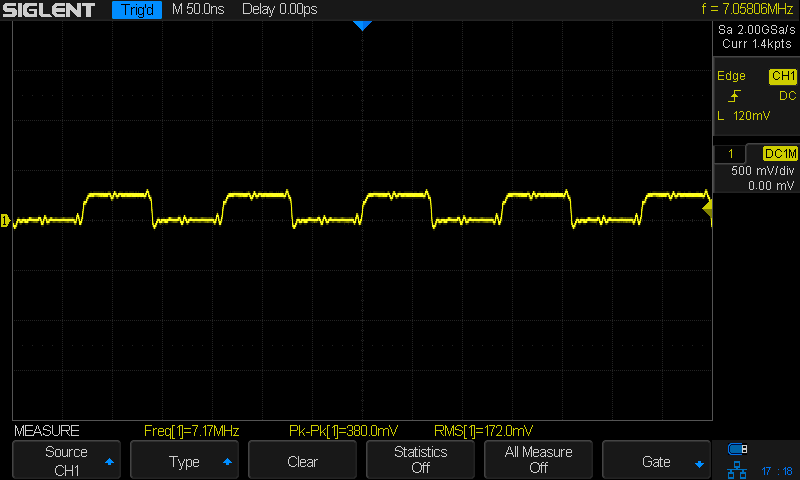

Here’s the 40 meter output, with the J3 jumper in place and the probe jammed into the header:

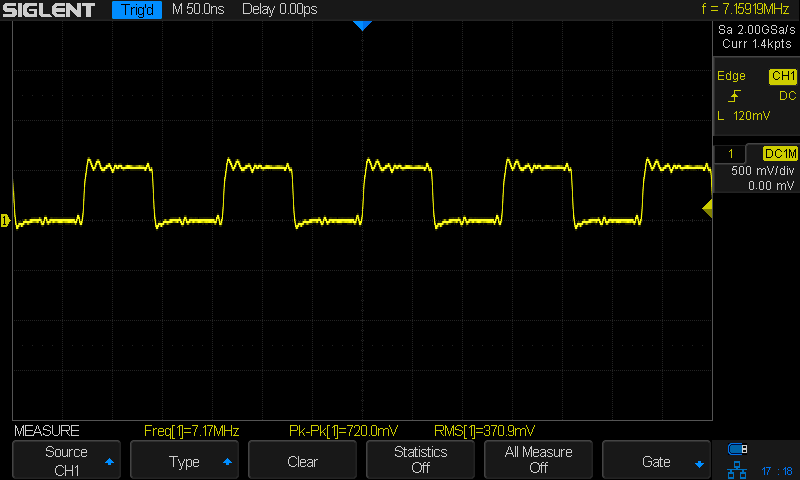

Pulling the J3 jumper off doubles the test signal amplitude:

Nothing wrong with those signals! In a pinch, those edges probably produce harmonics up in the UHF bands.

For completeness, here’s the 250 μA DC output driving a contestant chosen from the Box o’ Meters:

Eyeballometrically, the meter wants to see 1 mA for full-scale deflection, which is the whole point of the tester.

Recommended, with some early notes.